SK hynix et Intel présentent deux approches bien différentes pour atteindre un même but : augmenter la densité des puces des SSD et réduire les coûts. Le premier empile toujours plus de couches – il dépasse les 300 – tandis que le second grimpe à cinq bits par cellule, contre trois pour SK hynix.

L’été dernier, SK hynix et Micron annonçaient à tour de rôle de la 3D NAND avec respectivement 238 et 232 couches. Micron avait six couches de moins, mais était en avance sur son concurrent puisqu’il avait lancé la production en masse alors que SK hynix n’avait que des échantillons (samples) à l'époque.

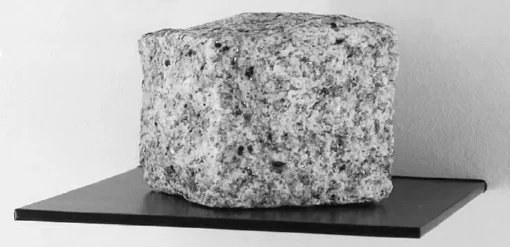

Il y a quelques semaines, lors de la conférence IEEE International Solid-State Circuits Conference (ISSCC) 2023, SK hynix est revenu sur le devant de la scène avec de la 3D NAND de 8e génération. Il grimpe cette fois-ci à plus de 300 couches, un record puisque les autres fabricants sont entre 232 et 238 couches, mais tous travaillent à augmenter ce nombre.

Pour le moment, il ne s’agit que d’une présentation technique avec un article intitulé « High-Density Memories and High-Speed Interface » signé par des ingénieurs de la société, comme le rapporte Blocks & Files. En plus de la densité, SK hynix annonce aussi des améliorations sur les performances. Explications.

SK hynix : densité et débits en hausse, latence en baisse

Le fabricant explique que ces puces TLC (trois bits par cellule) seront disponibles en version de 1 Tb (128 Go, il faut huit bits pour un octet), une capacité qui n'a rien d'exceptionnelle puisqu'elle était déjà prévue avec des puces de 238 couches. Et c'est sans compter qu'on retrouve aussi des puces de 1 Tb chez d'autres constructeurs.

Mais là où SK hynix écrase la concurrence, c'est sur la densité avec plus de 20 Gb/mm² (avec un b minuscule, il s'agit toujours de bits) avec plus de 300 couches, contre 11,55 Gb/mm² avec 238 couches. Selon Computer Base, la concurrence est aux alentours de 15 Gb/mm² maximum, la différence est donc bien significative.

Des améliorations sont par ailleurs apportées sur les débits, notamment avec une baisse de la latence du cycle de programmation de page interne (tProg) à 34 μs contre 45 μs sur la génération précédente de 2D NAND. Le débit en écriture par puce augmente sensiblement en passant de 164 à 194 Mo/s. SK hynix prend ainsi la couronne à Samsung qui était en tête jusqu'à présent avec 184 Mo/s sur sa 3D NAND V7. Pour le reste, pas de changement : une conception avec 4 plans, des pages de 16 ko et une interface entrées/sorties à 2,4 Gb/s.

De quoi ravir Seungpil Lee, vice-président du département NAND design de SK hynix : « Je crois que nous avons présenté les meilleurs densité et débit en écriture pour un produit TLC ». Il précise qu'empiler des couches n'est pas un simple jeu de construction : les couches doivent être de plus en plus fines, ce qui peut induire des erreurs et réduire les performances.

Intel reste à 192 couches, mais passe en PLC

Intel aussi profitait de cette conférence pour jouer de la surenchère sur la densité, avec pas moins de 23,3 Gb/mm². La technique pour arriver à ce résultat est bien différente. Il n'y a en effet « que » 192 couches, mais Intel exploite cette fois-ci de la NAND PLC (Penta Level Cell), c'est-à-dire avec 5 bits.

Comme à chaque fois que le nombre de bits par cellule augmente, cela a des incidences sur les débits et/ou la durée de vie. En effet, la PLC doit gérer correctement pas moins de 32 niveaux de tension. Il y en a pour rappel 2 en SLC (correspondant à 0 ou 1), 4 en MLC (00, 01, 10 et 11), 8 en TLC (000, 001, 010, 011, 100… jusqu'à 111), 16 en QLC (0000, 0001… 0010 jusqu'à 1111), etc. Intel affirme avoir mis en place des algorithmes dédiés pour limiter les problèmes, sans plus de précisions.

Les SSD TLC et QLC occupent une très grosse majorité du marché actuel. Les SSD PLC ne sont pas encore disponibles, mais cette technologie n'est pas nouvelle puisque des fabricants, dont Intel, planchent dessus depuis plusieurs années. La puce annoncée par Intel (3D NAND PLC, pour rappel) lors de la conférence ISSCC affichait une capacité de 1,67 Tb sur une superficie de 73,3 mm², ce qui donne bien une densité de 23,3 Gb/mm².

Le constructeur précise qu'il est aussi possible de l'utiliser en QLC ou en TLC, ce qui donnerait alors une densité de 18,7 et 14 Gb/mm² respectivement. Il faudra très probablement attendre la disponibilité des premiers SSD pour comparer les performances et l'endurance des puces en mode TLC, QLC et PLC.

Commentaires (24)

#1

Juste pour dire que j’adore tes articles hardware, à peu près autant que je déteste tes articles pas hardware. Ceci est un compliment empoisonné.

Ceci est un compliment empoisonné.

#2

Qui est ce qui s’équipe en SK Hynix derrière ? Certains couples j’ai : Intel/Micron/Crucial, Samsung/Samsung, …

WD ? Seagate ? Kingston ?

#3

J’ai trouvé drôle la parenthèse : « des échantillons (samples) », on sent la personne qui est tellement dans l’anglais qu’il en oublie quasiment le sens du mot “échantillon” :-) .

On pourrait faire pareil avec une partie de la phrase avant, voire tout le texte de l’article :

« mais était en avance (ahead) sur son concurrent (competitor) puisqu’il avait lancé (launched) la production en masse (mass production) »

#3.1

Haha alors non, c’est le cheminement inverse. Il y a certains mots que l’on va un peu plus pousser pour sortir des anglicismes, tout en précisant entre parenthèses le mot employé habituellement dans le “jargon”. Je fais la même chose avec cadriciel (framework)

#3.2

:-) je plussoie.

Cela dit, autant “cadriciel” c’est peu utilisé, autant “échantillon” c’est le mot qui me vient en tête, et c’est vraiment le même sens que “sample” (que ce soit pour “distribuer des échantillons” ou en traitement du signal, l’échantillonnage qui correspond à “sampling”). Je précise que depuis adolescent je lis une bonne partie des articles techniques en anglais.

#4

TLC (000, 001, 010, 011, 100… jusqu’à 111)

vs

TLC (000, 001, 010, 011, 100, 101, 110, 111)

Bravo, tu as gagné 2 caractères

#5

Les puces à 300 couches ont une durée de vie équivalente à celles avec moins, où ca la fait baisser un peu?

#6

Dire que si toute l’énergie, le pognon et les efforts de R&D consacrés au SSD avaient été dirigés dès le début sur une techno concurrente aux NAND, telle que 3D XPoint, on aurait aujourd’hui : des SSD encore plus rapides, qui ne s’usent quasiment pas dans le temps, et qui pourraient même dans certains cas remplacer la RAM.

Mais à l’heure ou je vous parle cette techno a été carrément abandonnée par ses deux inventeurs et promoteurs principaux : Intel et Micron.

Dans l’industrie, on n’aime pas trop les trucs solides, performants et inusables, par exemple il faut savoir que le CD audio, trop parfait, avait un certains nombre de détracteurs au sein de l’industrie, ce qui a retardé sérieusement sa sortie pour le grand public, dans les années 80, alors qu’il avait été pensé et élaboré au moins 10 avant, si ce n’est plus…

#7

Tu sais, si il y avait un réel attrait pour cette techno avec une fiabilité suffisante en production, la R&D aurait affiné les réglages.

“Dans l’industrie, on n’aime pas trop les trucs solides, performants et inusables”

Heu, ben tu connais un peu les procédés d’industrialisation justement ?

C’est l’art de rogner partout ou tu peux pour rendre un produit encore intéressant après cette étape, avec contrôle qualité toussa.

Parce que dans un labo, tu peux promettre un procédé qui fait (jusqu’à*) 1000x sur un point ou un autre, mais à quel prix ? fiabilité, perfs, yield de prod, qui a été sacrifié ?

ça accouche au mieux avec un 1.2x “pour l’instant” si tout se passe bien

Ton exemple sur le CD comme la VHS est complètement biaisé par le lobby des producteurs, pour les D.Durs ou les SSD c’est moins solide comme argument.

Après, Intel a toujours eu l’art de transformer en plomb tout ce qu’il achète, c’est le rôle de tout géant, digérer 95% de startups pour 5% qui aboutissent.

#7.1

Je me permet d’ajouter : le consommateur aime aussi les prix bas. Pour obtenir des prix abordables et quand même être rentable, il faut produire en masse.

Mais pour être vraiment rentable, il faut également que ton produit ne soit pas trop durable ni trop solide, parce que sinon le renouvellement n’est pas assez rapide pour t’assurer (et à tes actionnaires aussi), une rente régulière.

L’exemple qu’on cite souvent en plaisantant est celui d’Apple “il faut tout racheter” corp. Dans ce cas précis, la pression envers le client pour qu’il renouvelle son iMachin est plus subtile : même si le hardware de la firme est en général d’assez bonne qualité et relativement durable, ce n’est pas exactement le cas des logiciels qui l’anime.

A chaque nouvelle version des OS, de nouvelles incompatibilités arrivent, ce qui pousse l’écosystème, et j’y inclus les développeurs, à évoluer ou périr. Les investissements pour faire évoluer une application sont bien plus conséquents qu’avec d’autres familles d’OS, parce qu’à chaque fois il faut adopter un nouvel environnement de programmation (maintenant c’est Swift, mais dans deux ans, ce sera quoi ?), des frameworks sont supprimés et remplacés par d’autres, etc…

C’est subtil, mais cette pression stressante pour avancer à tout prix pèse sur les développeurs, et peuvent leur coûter un max en (auto-)formation, en mato\(, en embauche, etc... ne serait-ce qu'en temp\) !

Tout ça pour dire : personne n’a à gagner à fabriquer des produits non-périssables. Et un SSD NAND, avec l’augmentation exponentielle du nombre d’informations par cellule, et donc de sa fragilité, est le produit périssable par excellence.

Si d’autres firmes qu’Intel et Micron (exemple : Samsung) avaient pris le relais afin de développer des technos concurrentes, on aurait aujourd’hui des SSD ultra-robustes, garantis 30 ans minimum !

#8

Dans l’industrie, on aime ce qui se vend. Si les consommateurs (je trouve d’ailleurs que les 3 premières lettres du mot sont très parlantes quant au niveau de réflexion sur ce sujet) voulaient des supports de stockage qui durent 50 ans, ça se ferait et ça s’achèterait. Mais ça veut dire que ton SSD de 2 To acheté aujourd’hui sera toujours un SSD de 2 To en 2073. Tu crois que tu vas t’en satisfaire aussi longtemps ? Et il coûterait probablement 1000 ou 2000€ (pas un pb si tu le gardes réellement 50 ans, mais il faut pouvoir sortir les sous au moment de l’achat).

Si les consommateurs étaient capables de réfléchir aux conséquences indirectes de leurs achats, la plupart de nos problèmes environnementaux et climatiques seraient déjà en passe d’être résolus. Mais en fait, non, tout le monde s’en tape à partir du moment où ça implique de changer quelque chose au mode vie (même quand c’est peu), on se trouve des excuses pour ne rien faire (la France c’est 1%; de toute façon, le CO2 est nécessaire à la vie; et pis les riches, etc.)

#9

Pour ton SSD, il suffirait peut-etre de le re-flasher pour qu’il fonctionne en SLC.

Bon, ca lui fait perdre 32 fois sa capacite accessoirement, mais tu peux en mettre quelques grappes en RAID pour retrouver du volume, reprendre du debit et fiabiliser encore la data.

Apres, si tu regardes un peu du coté pro, il existe deja ces offres, mais tu ne vas pas mettre 5kE dans ton SSD, faut rester les pieds sur terre aussi. Les solutions SAN et autres pareil, le prix te fera reconsiderer ton besoin.

Tiens, vu que tu parles de “garantie 30ans”, remet toi dans l’epoque 1993. Tu avais quoi a l’epoque ? du floppy, voir un Disque de 20Mo 5p1/4 ou il fallait parquer les tetes pour ne pas le rayer. Si tu l’as garde il y a des chances qu’il fonctionne encore. Par contre son ratio conso/kb est assez mauvais.

Meme les batiments n’ont pas de garantie tri-decenale

#10

Tu n’en sais rien du tout.

Heu…

Tu racontes n’importe quoi.

L’enregistrement numérique lui existait avant la mise sur le marché du CD, mais ce n’est pas pour des considérations comme celles que tu cites. Il faut savoir que les meilleurs enregistrements analogiques (sur bandes) étaient déjà bien meilleurs que ce qu’on arrivait à transcrire sur microsillon, rien que la numérisation d’un “master” analogique sur CD était excellente (les CD “AAD” et “ADD”).

Apparemment pas…

Heu, rien à voir.

Quand le CD est sorti, les mélomanes (ceux qui écoutent du classique généralement, voire du jazz) se sont précipités sur ce média, vu l’énorme gain qualitatif. Il fallait quand même acheter un nouveau lecteur donc ce n’est pas instantané non plus.

#11

Je pense que tu n’as jamais entendu parler de Leica, Miele, Mercedes, et d’autres marques pas forcément allemandes.

Et si, et ils le font.

Tu racontes vraiment n’importe quoi. Les SSD sont plus fiables que les disques durs magnétiques, donc moins fragiles.

Mais tu n’en sais absolument rien, et c’est très probablement faux.

Sans parler du fait qu’une garantie de 30 ans ne sert absolument à rien en informatique, aucun matériel n’est utilisé aussi longtemps, et certainement pas les disques, qui sont changés bien avant.

#11.1

Concernant les nouvelles NAND, je cite l’article :

Plus loin :

Je t’invite à lire attentivement cet article détaillé (vu du point de vue de l’industrie) sur la techno 3D Xpoint, ainsi que la remarquable page Wikipedia en anglais sur cette techno très intéressante, malheureusement abandonnée par Intel et Micron.

Et enfin, un dernier article concernant la durée de vie de nos SSD actuels, là aussi je cite :

Cette nette diminution des cycles d’écriture-effacement, de l’endurance, à cause de la densité toujours plus grande des infos par cellule, est ce que j’appelle “fragilité” et “manque d’endurance”. Le SSD est donc pour moi un produit périssable.

#12

Malgré plusieurs personnes qui t’ont expliqué les tenants et aboutissants, tu persistes.

Le SSD n’est pas plus “périssable” qu’avant, les SSD sont plus fiables que les disques durs magnétiques, on en connaît l’endurance (selon la mise en oeuvre) et sauf panne (car on n’est jamais à 100 % de fiabilité) ont des durées de vie telles qu’on les change avant qu’ils ne soient inutilisables (cellules trop usées).

Quand à la 3D XPoint, ce n’est parce que ça a l’air mieux que ça l’est en pratique. L’histoire de la technique est pleine de ce genre de chose.

#12.1

Je comprends les différends arguments présentés, (et le fait que quelque soit la densité, certains fabricants garantissent leurs SSD jusqu’à 5 ans) mais ayant lu plusieurs articles techniques depuis les balbutiements de la techno NAND, je ne peux m’empêcher de trouver cette techno bancale, elle est à l’opposé de la robustesse que j’attends (dans mes rêves, d’accord…) d’un système sans aucune partie mobile, composé uniquement de chips mémoire…

Le fait que les informations que tu mets dessus s’effacent au bout d’une certaine période, comme une bande magnétique exposée à des champs un peu trop violent, ou encore ces vieilles disquettes qui s’effaçaient toutes seules au bout d’un an ou deux si tu ne rafraîchissait pas les informations sauvegardées dessus (en gros et pour résumer : une disquette que tu n’utilisais pas régulièrement avait tendance à perdre ses infos).

Ma référence à moi, c’est que bien avant les SSD, des fabricants proposaient des cartes PCI avec dessus de la mémoire (S)DRAM classique, alimentée en permanence par une batterie. Si je me souviens bien, ces cartes comportaient des condensateurs, qui prenaient le relais en cas de panne, de micro-coupure ou de changement de batterie.

Bien évidemment je ne dis pas que ce système était parfait (il était cher, parce que pas produit en masse comme les HDD), je dis juste que tant que ces barettes de RAM étaient alimentées, elles conservaient tes informations indéfiniment, sans aucune limite de temps. Tu pouvais compter sur elles.

#13

Tu as lu ça où ? C’est tout simplement faux.

Jamais eu ce cas. Il n’y aucune raison qu’une disquette perde ses informations si elle est conservée correctement.

Ça existe depuis bien avant des cartes PCI avec de la RAM, les contrôleurs sur batterie (ou les disques avec des condensateurs assez gros pour finir d’écrire en cas de coupure). Ça existait déjà avant 2000.

#13.1

Je te parle justement de cette période, je suis de la vieille école, 60 ans bien tassés, merci pour lui…

Le fait est que j’ai essayé de relire mes anciennes séquences (j’ai gardé mon vieux séquenceur Yamaha sur lequel, bien avant de posséder un ordi, je créais et sauvegardait mes musiques, mes arrangements, compos, etc… en MIDI), et bien que conservées très précieusement, ces disquettes 1.44” se sont avérées toutes illisibles. En fait, l’appareil les voyaient toutes comme des disquettes vierges.

Un ami spécialiste des vieilles technos (il faisait de la maintenance et des réparations d’ordis, dans le temps) m’a expliqué alors que les infos sauvegardées sur disquettes ont besoin d’un rafraîchissement régulier, faute de quoi il arrive ce qui m’est arrivé. Après bon, si tu me crois pas c’est pas grave, je retourne à mes moutons musicaux…

#14

Même un disque dur perd ses données s’il n’est pas alimenté (ou les données pas rafraichies) au bout de nombreuses (très très nombreuses) années. La question comme à chaque fois: est-ce que cela impacte l’usage prévu? Dans ce cas bien prévoir d’utiliser une techno adaptée à l’usage…

#15

Juste sur ce point : connaissant la fragilité du bouzin je faisais très attention à mes disquettes. Et pourtant, j’ai perdu un certain nombre d’archives RAR parce-qu’elles étaient découpées en 10 disquettes et que la 4e/5e/6e présentait des erreurs de lecture.

Et je ne parle pas seulement des disquettes 720k percées pour les faire passer à 1.44Mo

#16

Tu as une source ?

Parce qu’en plus un disque dur est dans une cage de Faraday, et heureusement qu’on relit le MBR après plein d’années, le MBR n’étant que rarement modifié.

Je n’ai jamais lu qu’il fallait rafraîchir des données sur un disque dur.

Du fait qu’il y avait contact physique entre la tête de lecture et la surface du disque, ça s’usait plus facilement qu’un disque dur.

Je ne me souviens pas avoir perdu du contenu sur des disquettes.

Ces pertes se sont produites après combien d’années ?

#17

Euh… honnêtement…? Je me souviens juste de la frustration de ne pas pouvoir lire certains trucs (sans doute un jeu quelconque que j’avais dû sortir de mon disque dur de 80Mo pour faire un peu de place). Mais comme c’était il y a une petite trentaine d’années, ça sera compliqué de te donner des détails plus précis

#18

Bonne question. J’avais compris que la 3D Nand avait permis justement d’arrêter de faire des cellules de plus en plus petites horizontalement, entrainant des erreurs. Mais si on fait des couches de plus en plus fines, on risque de retrouver le même problème.

La technique à 5 bits d’Intel, avec ses niveaux de tension peu espacés, ne m’inspirent pas trop non plus sur ce problème de fiabilité.