Des chercheurs d'IBM affirment avoir mis au point une puce « 25 fois plus efficace énergétiquement » qu'un GPU pour faire tourner un réseau de neurones, dans certaines conditions bien évidemment. Plusieurs questions restent autour de cette puce spécialisée – baptisée NorthPole – qui n’est pas un produit prêt à être commercialisé.

Une équipe de chercheurs d'IBM, menée par Dharmendra Modha (employé par la société depuis près de 27 ans), s'est appuyée sur une modélisation plus récente du cerveau humain pour créer une puce qui se passe de mémoire RAM. Plus exactement, elle intègre directement la mémoire au niveau des unités de calcul, la rendant bien plus efficace énergétiquement. Les chercheurs ont publié la description de NorthPole dans la revue scientifique Science.

Sur un benchmark comparant les performances de puces faisant tourner le réseau de neurones spécialisé dans la reconnaissance d'images ResNet50, leur processeur NorthPole serait 25 fois plus efficace que des GPU gravés en 12 nm. Pourquoi prendre 12 nm alors que les GPU actuels sont en 4/5 nm ? Tout simplement car NothPole est, elle aussi, gravée en 12 nm. L’article de Science met aussi en avant une meilleure densité avec « 5 fois plus de FPS par transistor », et une latence 22 fois plus basse.

Dharmendra Modha ajoute que, toujours sur ResNet-50, « NorthPole surpasse toutes les principales architectures courantes, même celles qui utilisent des processus technologiques plus avancés, comme un GPU implémenté à l'aide d'un processus 4 nm ». Cette fois par contre, aucun chiffre n’est précisé.

von Neumann : un goulot à éviter

Jusqu'à maintenant, les architectures informatiques classiques restent basées sur une modélisation dite d'« architecture de von Neumann » avec une séparation entre trois éléments : une unité arithmétique et une unité de commande dans le processeur, ainsi qu'une mémoire contenant les programmes et les données.

Mais cette séparation de la mémoire et de l'unité de traitement suppose énormément de transferts de données sur un bus dont le débit serait désormais un facteur limitant. Ce phénomène est appelé « goulot de von Neumann », et il est d'autant plus problématique pour les réseaux de neurones qui manipulent beaucoup de données. Ils consomment actuellement beaucoup plus d'énergie pour cette manipulation que pour du calcul.

Depuis quelques années, les chercheurs tentent de passer outre en rapprochant au plus près la mémoire de l'instance de calcul, comme dans le cerveau humain ou des macaques. Certains essayent aussi de créer des mémoires à l'échelle nanométrique inspirées du système nerveux des insectes, comme Elisa Vianello, chercheuse du CEA-LETI.

La mémoire au plus proche des unités de calcul

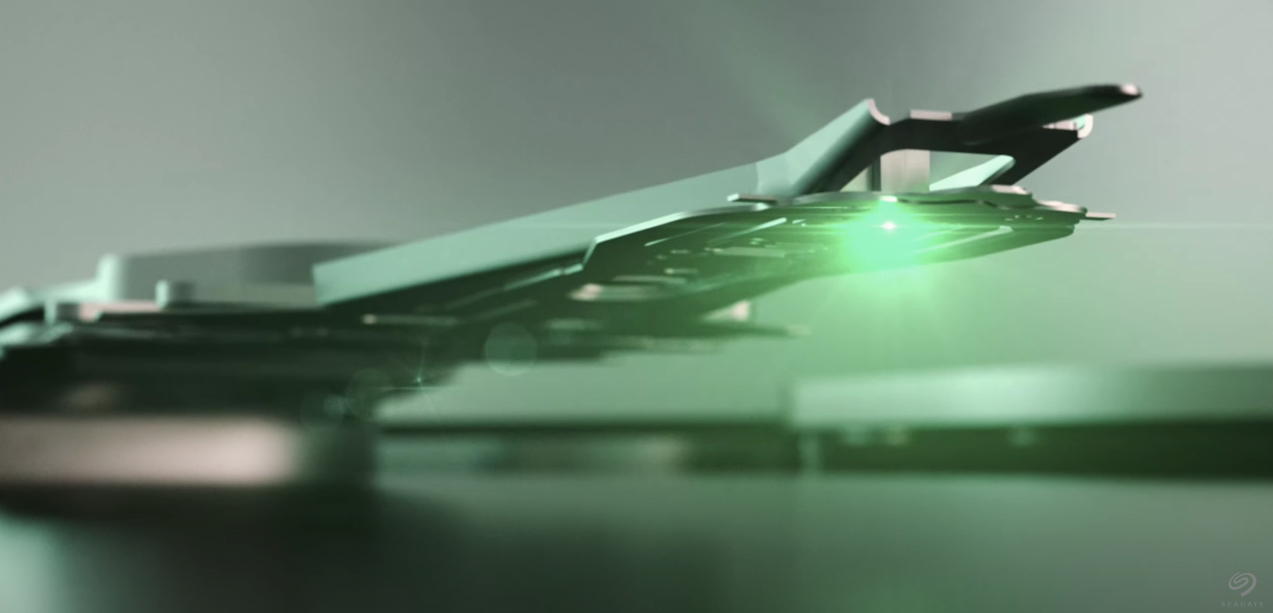

Après des années d'effort, l'équipe d'IBM présente donc sa puce, NorthPole, qui reste un travail de recherche et est encore loin d'être industrialisable. Mais elle propose une réduction significative de la consommation énergétique. Dans ce système, toute la mémoire utilisée par le processeur est incluse directement sur la puce.

Dans la publication scientifique, on retrouve un graphique permettant de comprendre l’agencement de la mémoire et des unités de calculs, et les différences entre les différentes technologies.

Dans les GPU et les CPU, les différents niveaux de cache placent de la mémoire plus ou moins proche des unités de calculs, mais en petites quantités. La grosse partie de la mémoire est partagée. Sur les TPU, davantage de mémoire est intégrée dans les unités de calcul, mais il en reste toujours beaucoup en dehors. Avec NorthPole, IBM pousse le concept à son paroxysme : chaque unité de calcul dispose de sa propre mémoire, avec 768 ko par cœur. À cela, s’ajoutent 32 Mo de mémoire tampon pour les entrées/sorties.

Efficacité énergétique « époustouflante »

NorthPole a été gravée en 12 nm et comporte 22 milliards de transistors sur une surface de 800 mm². IBM est quasiment au même niveau de densité que les GPU Turing de NVIDIA, avec 18,6 milliards de transistors sur 754 mm². Mais cela n’a rien d’exceptionnel par rapport à ce que propose le fabricant de cartes graphique aujourd’hui. En effet, avec sa puce Ada Lovace (GeFoce RTX 40) il grimpe à 76,3 milliards de transistors sur 610 mm², soit une densité de plus de 125 millions de transistors par mm².

Quoi qu’il en soit, NorthPole comporte 256 cœurs qui peuvent effectuer 2 048 opérations par cycle à 8 bits de précision (4 096 sur 4 bits et 8 192 sur 2 bits). Mais surtout, elle intègre un total de 224 Mo de mémoire : 768 ko par cœur et un framebuffer de 32 Mo. Oui, le compte est bon : 256 x (768/1024) + 32 = 224.

La première implémentation de cette puce est disponible sous la forme d’une carte au format PCIe. IBM ajoute que, sur le réseau de référence ResNet50, « NorthPole peut fonctionner à des fréquences allant de 25 à 425 MHz ».

La puce d’IBM est optimisée pour une précision faible de 2 à 8 bits seulement. Selon le constructeur, « cela suffit pour obtenir une précision d'inférence de pointe sur de nombreux réseaux neuronaux, tout en se passant de la haute précision requise pour l'entraînement », est-il précisé dans l'article.

« Son efficacité énergétique est tout simplement époustouflante », commente le chercheur en nanoélectronique du CNRS Damien Querlioz, interrogé par la revue Nature. « Je pense que cet article va ébranler les idées reçues en matière d'architecture informatique », rajoute-t-il.

Attentions aux unités des graphiques

Quand on regarde les graphes de comparaison ci-dessous avec des CPU, des GPU et des accélérateurs (pêle-mêle : CPU Xeon, GPU A100/H100, Jetson, TPU) les performances du nouveau processeur d'IBM ont de quoi impressionner car NorthPole se retrouve seule en haut à droite… mais attention à bien lire les graphiques.

Dans le premier (A), il est question de « space metric » sur l’axe des ordonnés, c’est-à-dire des « FPS par milliard de transistors ». Sur les abscisses, on retrouve « energy metric » soit des « FPS par watt ». Pour simplifier : à performances identiques, moins une puce a de transistors pour effectuer une tâche, plus elle se place dans le haut du tableau.

Sur un bench donné, une puce spécialisée avec moins de transistors se placera donc toujours au-dessus d’une puce généraliste. Elle est en effet optimisée pour ce travail et tout le superflu est enlevé. C’est un peu comme comparer une puce capable de faire uniquement des additions à une autre capable aussi de réaliser des multiplications : sur un test d’addition seulement, la première s’en sortira largement mieux.

Même chose avec la consommation électrique. C’est un peu comme comparer les performances/transistors et les performances/watt d’un asic uniquement capable de miner des cryptomonnaies et d’un GPU, qui est également capable de faire tourner des jeux, des réseaux de neurones, etc.

Une puce très spécialisée

Dans leur article, les chercheurs précisent dix axiomes concernant NorthPole, notamment que cette puce est spécialisée dans l'inférence neuronale. « Par exemple, il n'a pas de branchement conditionnel dépendant des données, et il ne prend pas en charge l'entrainement ou le calcul scientifique », expliquent-ils.

De plus, comme le reconnait IBM dans son communiqué, « le plus gros avantage de NorthPole [sa mémoire intégrée, ndlr] est aussi une contrainte : il ne peut exploiter facilement que de la mémoire dont il dispose ». En effet, si les unités de calcul doivent accéder à des informations se trouvant ailleurs, « toutes les accélérations possibles sur la puce seraient compromises ».

Techniquement, NorthPole pourrait « prendre en charge des réseaux neuronaux plus grands en les découpant en sous-réseaux plus petits, chacun s'intégrant dans la mémoire […] et en connectant ces sous-réseaux sur plusieurs puces ». Mais IBM le reconnait dans son communiqué : « cette puce n'est pas censée être un touche-à-tout ». On aurait aimé avoir plus de détails sur ce qu’il est possible de faire dans la pratique avec 256 x 768 ko de mémoire.

Dharmendra Modha abonde : « Nous ne pouvons pas y exécuter GPT-4, mais nous pourrions répondre à de nombreux modèles dont les entreprises ont besoin […] Et bien sûr, NorthPole est uniquement destinée à l'inférence ». Partant de là, il est dommage de la comparer aussi frontalement dans la communication à des CPU et GPU, des comparaisons avec les TPU de Google par exemple auraient été plus utiles.

Il reste également la question du prix, qui n’est pas évoquée dans les différentes publications. C’est souvent le nerf de la guerre, avec les performances et la consommation. Dans tous les cas, « ce n’est que le début du travail de Modha sur NorthPole », affirme IBM en guise de conclusion. Une première optimisation serait certainement d'augmenter la finesse de gravure et d’attendre quelques nm.

Commentaires (6)

#1

Il sert à quoi le Xillinx virtex ?

#1.1

Des supposition de ma part :

Je pense que le FPGA sert à gérer les interfaces. En gros un sorte de “North Bridge”/ chipset connecté à leur puce.

Sur nos cartes mères, ce sont des puces dédiées pour des économie d’échelles (sur des Millions exemplaires). Ici nous somme sur du “proto”, bien inférieur au Million exemplaires.

Ou même, pour ne pas limiter les interfaces envisageables ? Ou les deux ?

#2

J’allais poser la même question.

Ca semble être un VU5P - donc pas une petite bestiolle

#2.1

Comme cité plus haut, le FPGA doit servir de “glue logic” pour pouvoir interfacer la puce “relativement facilement ” en attendant de finaliser la puce d’interface qui sera produite par lithographie.

Sachant que un gros FPGA comme ça peut faire simultanément SOC, north bridge, mémoire RAM, générateur d’horloges ….

#3

Ca se rapproche du “In memory computing”.

L’architecture avec un CPU central est on goulot d’étranglement - pas par sa vitesse de calcul, mais plutôt par son nombre de canaux, et l’architecture qui consiste à lire en mémoire et y réécrire après le calcul.

Le rendu graphique a permis de s’orienter vers la super-parallélisation.

L’IA va certainement aller vers d’autres types d’architectures, notamment sur l’accès mémoire (lecture puis écriture séquentielle “plus loin”).

Un peu comme les puces mémoires de certaines TV milieu 90 qui permettaient de lire en ligne et d’écrire en ligne en même temps.

Mais surtout, ça me fait penser que les “accélérateurs” d’IA (NPU, KPU et autres) actuellement intégrés aux appareils dans les CPU et SOCs et annoncés à grand renfort de marketing risquent bien d’être vite inutiles et inutilisés en cas de changement d’algo/de paradigme (c’est déjà le cas, la plupart de ces unités ayant des limites de fait qui ne sont pas contournable “localement”)

#4

Avec NorthPole et ses performances extraordinaire, IBM essaierait-il de nous faire croire au Père Noël ?