Il y a quelques jours, SK hynix annonçait de la 3D NAND avec plus de 300 couches. Aujourd'hui, c'est au tour de Kioxia et Western Digital de présenter leur nouveauté avec de la 3D NAND à 218 couches « seulement ». Les deux partenaires mettent en avant une nouvelle technologie CBA et annoncent des débits supérieurs à la concurrence.

Depuis maintenant plusieurs années, les fabricants empilent toujours plus de couches afin d'augmenter la densité de leurs puces. De quelques dizaines, ils sont passés à des centaines de couches au fil des générations de 3D NAND. Kioxia et Western Digital en sont ainsi à leur 8e génération... mais ne cherchez pas la 7e, elle a tout simplement été abandonnée en route.

Alors que la BiCS de 7e génération (ou BiCS+) devait exploiter une architecture avec 212 couches, celle de 8e génération du jour en comporte 218. Elle prend donc le relai de la 6e génération et ses 162 couches (vous suivez ?). Kioxia et Western Digital sont ainsi légèrement en dessous de Micron (232 couches), Samsung (236 couches) et SK hynix (238 couches, des puces à +300 arriveront plus tard).

La BiCS passe en mode « sandwich », comme YMT l'avait déjà fait

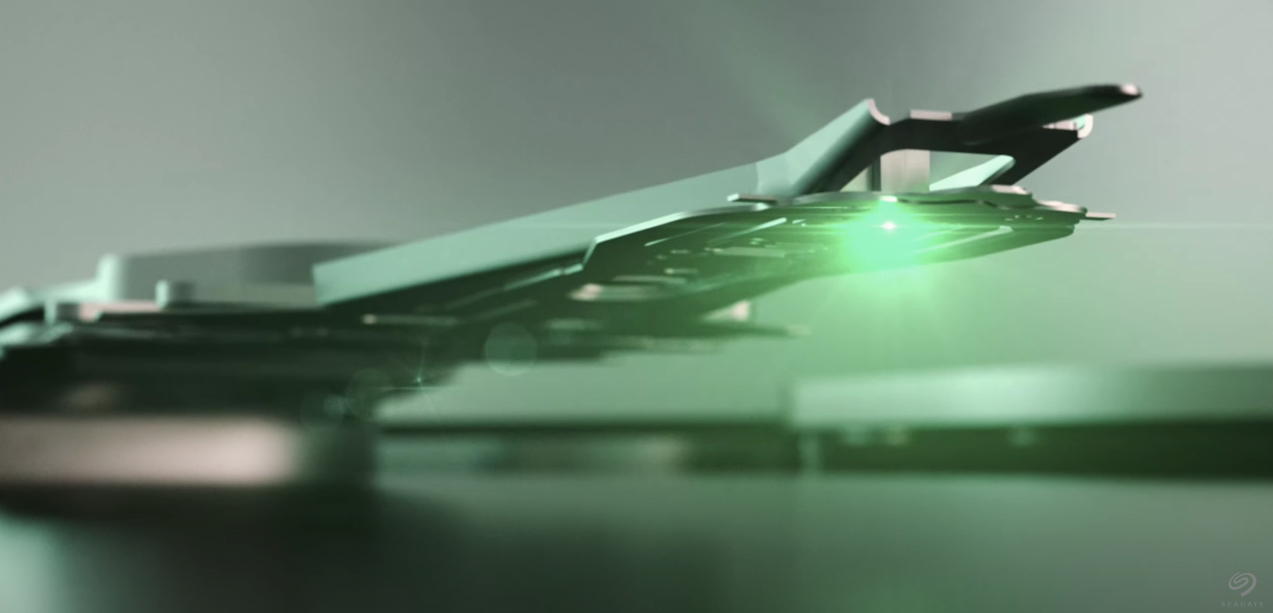

Pour développer leurs puces, les deux partenaires du jour exploitent une nouvelle technologie baptisée CBA (CMOS directly Bonded to Array). Dans la pratique, il s'agit de concevoir séparément les matrices de cellules de NAND (pour le stockage des données) et la partie CMOS (avec les entrées/sorties). Deux wafers différents sont utilisés, avec des procédés de fabrication optimisés dans chaque cas. Les deux parties sont ensuite « collées » ensemble pour former la puce de NAND.

Cet assemblage n'est pas une nouveauté dans le monde de la 3D NAND. Yangtze Memory Technology (YMT) présentait en effet son procédé Xstacking lors du Flash Memory Summit de 2018. Le principe de base était exactement le même : utiliser deux wafers à la place d'un seul. Un pour le circuit logique, l'autre pour les cellules devant stocker les informations.

Des puces de 1 Tb, en TLC ou QLC

WD et Kioxia indiquent qu'ils proposeront des puces avec une capacité de 1 Tb, aussi bien en TLC (trois bits par cellule) qu'en QLC (quatre bits par cellule). Les deux constructeurs mettent également en avant une « technologie innovante de rétrécissement latéral ». Combinée avec la hausse du nombre de couches, cela permet d'augmenter « la densité des bits de plus de 50 % ».

Aucune précision technique n'est donnée concernant ce « rétrécissement latéral » ; et c'est bien dommage, car il participe de manière significative à augmenter la densité. Si l'on ne prend en compte que le nombre de couches, la hausse de densité ne serait « que » de 35 % environ (162 à 218).

Pour rappel, SK hynix revendique la couronne de la densité avec une puce à de plus de 20 Gb/mm² pour sa 3D NAND de plus de 300 couches, contre 11,55 Gb/mm² avec celle de 238 couches. WD et Kioxia ne communiquent pas sur ce chiffre, mais revendiquent (selon leurs propres analyses) « la densité la plus élevée de l'industrie », selon Masaki Momodomi, directeur de la technologie chez Kioxia.

Plus de 3,2 Gb/s, bien au-delà de la concurrence

Les débits aussi progressent avec plus de 3,2 Gb/s par puce, soit 60 % de plus que la génération précédente qui était à 2 Gb/s (BiCS de 6e génération), selon les mesures des deux fabricants. C'est largement mieux que SK hynix, dont les dernières puces de 3D NAND sont à 2,4 Gb/s, comme la génération précédente.

Lors de l'annonce du Xstacking en 2018, YMT affirmait que ces puces pourraient atteindre 3,0 Gb/s, alors que les autres fabricants étaient à l'époque entre 1 et 1,4 Gb/s au maximum. Aujourd'hui les puces de 3D NAND sont entre 2 et 2,4 Gb/s chez les constructeurs, la nouvelle BiCS marque donc bien le pas.

Enfin, la latence aussi est améliorée au passage, mais encore une fois sans plus de précision.

Les premiers échantillons de BiCS de 8e génération sont disponibles pour des partenaires triés sur le volet. WD et Kioxia pensent que leurs puces seront particulièrement utiles dans les smartphones, les objets connectés et les datacenters.

Commentaires (6)

#1

Be be suits peut-être plus à la page, mais les TLC et QLC c’est pas censé être moins fiable que les MLC et SLC ?

#2

Si, mais pas au point d’être vraiment gênant pour un usage classique d’utilisateur lambda.

Par contre, j’aurais bien aimé un petit rappel sur la signification de BiCS.

#3

Je propose des gaufrets (ou gaufrettes) en français

#4

#5

Les débits c’est en séquentiel ou aléatoire?

#5.1

C’est le débit par pin il me semble