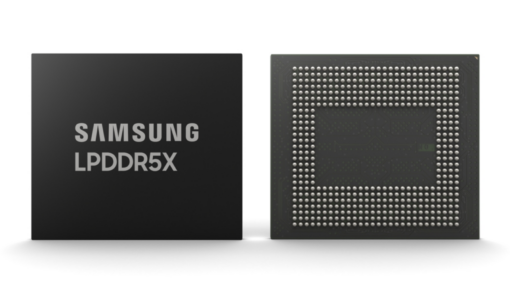

Cette semaine, c'est le RISC-V Summit. Plusieurs constructeurs et partenaires de la fondation font ainsi des annonces et des démonstrations, de nombreuses vidéos devant être diffusées par ici.

C'est Imagination Technologies qui a ouvert le bal avec ses Catapult, proposés en 32 ou 64 bits, avec de nombreuses options pour s'adapter aux besoins de différents marchés et de différents clients précise l'entreprise. Ils sont accompagnés du Catapult SDK et de Catapult Studio, basé sur Visual Studio Code.

Le SDK comporte des versions adaptées des compilateurs GCC, LLVM et GDB, ainsi que de bibliothèques C optimisées. Il est distribué pour CentOS, macOS, Ubuntu et Windows, gérant tant FreeRTOS que Linux avec des bootloaders et des noyaux de référence, ainsi que des systèmes de fichiers basés sur Yocto.

Plusieurs familles seront proposées, chacune étant plus complète que la précédente :

- Dynamic microcontrollers

- Real-time embedded CPUs

- High-performance application CPUs

- Functionally safe automotive CPUs

Les premiers sont d'ores et déjà disponibles et livrés à certains clients au sein de GPU intégrés à des SoC pour le marché automobile. Imagination précise d'ailleurs que ses solutions RISC-V sont certifiées ISO 26262 et peuvent s'adapter aux différents niveaux d'Automotive Safety Integrity Level (ASIL).

Les seconds sont eux aussi disponibles pour les clients de l'entreprise qui précise que les deux derniers ne seront proposés qu'à partir de l'année prochaine, sans plus de précisions. Des documentations sont disponibles par ici. Notez que ce n'est qu'un début, Imagination évoquant déjà de prochaines générations.

Commentaires (11)

#1

Je peux pas m’empécher de penser à un épisode de Kaamelott…

Bon, je vais lire l’article maintenant ^^’

#2

Ce sous titre

va lire l’article

#3

RISC-V ISA.

ISA sérieusement ????

https://fr.wikipedia.org/wiki/Bus_ISA_(Informatique)

Et dans quelques mois des RISC-V PCI ?

-> Je deviens devin (facile de prévoir le futur, quand il a déjà eu lieu chez ses concurrents !!!) :)

#4

ISA : Instruction Set Architecture

#5

Est-ce qu’un 32 bits massivement parallèle est dans les tuyaux ? 256 cœurs par exemple ?

#6

Et bin quel est le problème ?

https://en.wikipedia.org/wiki/Instruction_set_architecture?wprov=sfla1

#7

ISA = Instruction Set Architecture, non ?

burned

#8

Avoir perdu une occasion… de se taire! Et avoir connu l’époque de l’IBM-PC originel…

#9

Ma maman me disait toujours de tourner ma langue 7 fois dans ma bouche avant de parler…

#10

Excellent le sous-titre

#11

+1 pour le sous-titre !!!