L'initiative CXL commence à se concrétiser. Les partenaires multiplient les annonces et Samsung dévoile un premier produit qui devrait en intéresser plus d'un : un module de DDR5 sous la forme d'un boîtier enfichable.

Alors que la DDR5 et le PCIe 5.0 devraient se généraliser à partir de la fin de l'année, il y a un autre standard qui devrait être exploité de manière croissante, notamment dans les datacenters : Compute Express Link (CXL).

Il s'agit d'une solution d'interconnexion basée sur PCIe 5.0 mais optimisée pour faciliter les accès directs à basse latence aux données en mémoire, leur cohérence, etc. Annoncée il y a deux ans par Intel et plusieurs partenaires, elle s'est depuis accordée avec un autre consortium proposant une solution similaire : Gen-Z. De quoi permettre sa montée en puissance, ARM prévoyant par exemple d'utiliser CXL au sein de ses prochaines générations.

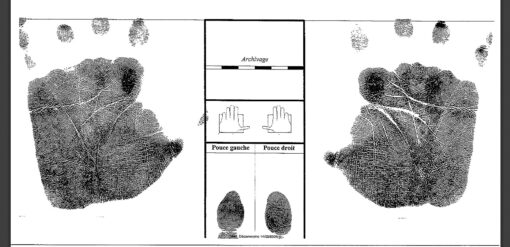

Aujourd'hui, c'est au tour d'un autre membre fondateur de Gen-Z d'annoncer un produit CXL : Samsung. La société dévoile ainsi un module de DDR5, qui ne prend pas la forme de barrettes à utiliser dans des emplacements DIMM, mais d'un boîtier pouvant être connecté directement à une interface CXL. AMD et Intel sont partenaires de l'initiative.

Samsung dit avoir « intégré différents contrôleurs et solutions logicielles comme le mappage mémoire, la conversion d'interface et la gestion d'erreurs, permettant aux CPU ou GPU de considérer et d'utiliser la mémoire CXL comme de la mémoire système ». L'idée est ainsi de ne plus être dépendant du nombre de canaux mémoire gérés par le processeur et de pouvoir ajouter une quantité plus importante de mémoire au sein d'un système, comme Intel le fait à sa manière avec ses modules Optane PMem à mi-chemin entre mémoire et SSD, mais au format barrette DIMM.

Samsung n'a pour le moment livré aucune donnée technique concrète sur ce produit : latence, débit ou même quantité de mémoire présente au sein de chaque module. Le constructeur promet néanmoins qu'il permettra « d'atteindre le niveau du To », ce qui nécessite actuellement 16 modules de 64 Go sur un système classique.

On devrait en savoir plus lorsqu'il commencera à arriver chez des clients et à être mis sur le marché.

Commentaires (10)

#1

Très intéressant, hâte de voir ce que ça donnera niveau performances :)

#2

PCIe 5 ? Intel vient tout juste de sortir du PCIe 4 sur leurs dernier proc et on passe déjà au 5 ?

#3

Comme dit, le PCIe 5.0 est prévu pour les prochaines plateformes depuis longtemps : Alder Lake et Sapphire Rapids (Intel), Zen 4 (AMD), les prochaines Neoverse pour ARM. Ici, ce sont des produits de datacenter, où ces interconnexions sont en avance de phase par rapport au grand public parce que le besoin y est important et donc la migration rapide. Et le PCI Express est désormais sur un rythme d’une versions tous les deux ans, avec le PCIe 6.0 déjà en préparation pour rappel ;)

#4

Pour préciser ce que dit David, Alder Lake-S devrait débarquer avant la fin de l’année, donc le PCI-E 5.0 va se concrétiser assez rapidement côté Intel, effectivement moins de 9 mois après l’arrivée du PCI-E 4.0 sur leurs plateformes.

#5

Un peu plus si tu comptes Tiger Lake ;)

#6

Ok, j’avais loupé l’info. Mais assez surpris vu le temps qu’on est resté sur la v3

#7

AMD ça fait presque deux ans qu’ils ont intégrés le PCI-e 4.0 dans leurs plateformes

#8

#9

Ne jamais oublier une chose qui est à mon sens l’intérêts principal des nouvelles normes sur les plateformes grand public : on fait le même débit avec deux fois moins de lignes.

Comme le nombre de lignes PCIe a tendance à stagner, le passage à une nouvelle version de la norme permet de doubler la capacité à nombre de lignes constant, et donc les différentes possibilités. Par exemple une solution x4 + x4 + x4 + x4 en PCIe 5.0 sera comme du x16 + x16 + x16 + x16 en PCIe 3.0.

#10

C’est amusant comme on revient aux architectures où tout se partage le même bus.

Au début de l’informatique ça se passait comme ça, le processeur accédait au même bus pour à peu près tout. Et finalement la carte mère c’était surtout des connecteurs et des pistes.

Puis on a créé des bus séparés et spécialisés car le bus unique devenait un goulot d’étranglement.

Revenir à un bus unique ultra rapide sera peut être un grand retour à la souplesse originelle. On ne sera peut être plus limités par la carte mère si on veut rajouter de la RAM au delà du nombre de slots DIMM