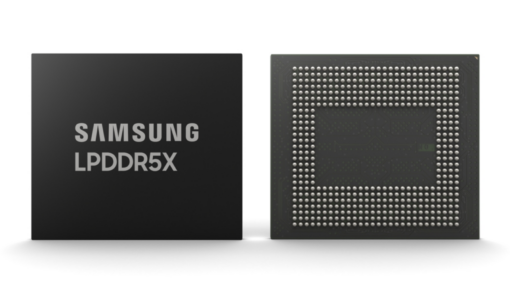

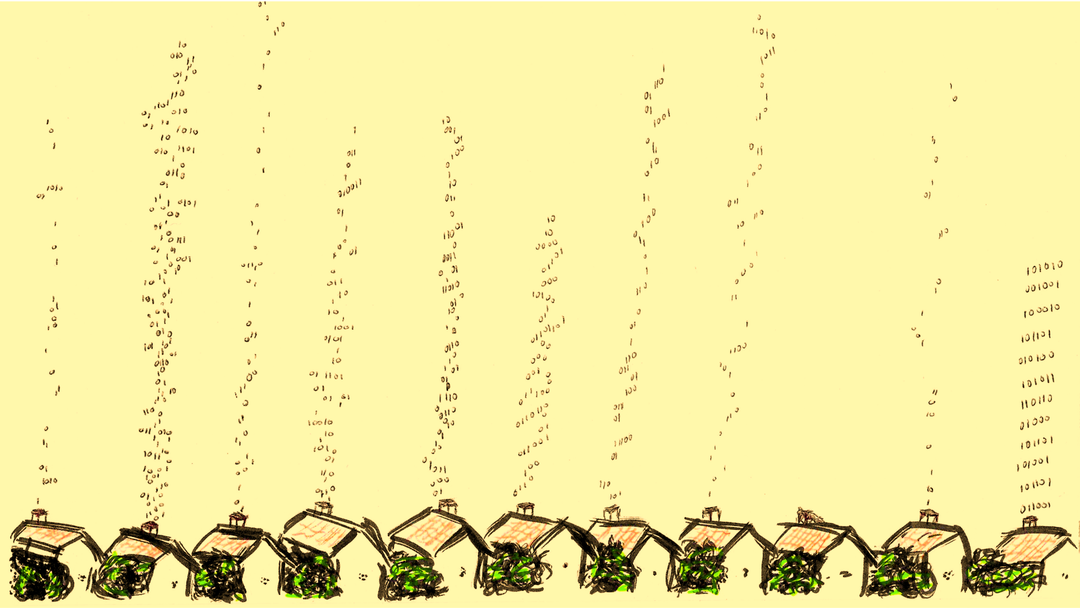

Petit à petit, les accélérateurs se rapprochent des sources de données. C'est le cas avec les SmartSSD, où Xilinx se place directement dans un périphérique de stockage Samsung.

Samsung avait déjà présenté son SmartSSD – dans la famille des Computational Storage Drive (CSD) – fin 2018. Il était alors question d’une carte PCIe. Le fabricant revient avec une nouvelle version, sous la forme d’un SSD de 2,5" en U.2.

Il propose pour le moment 3,84 To de stockage via de la V-NAND de Samsung, sans plus de précision. Mais l'on sait d'ores et déjà que d’autres capacités suivront. Les débits sont de 3,5 Go/s en lecture et 3,2 Go/s en écriture (respectivement 800 et 135 kIOPS), avec une endurance de 1 DWPD (Drive Write Per Day) pendant cinq ans.

Une puce KintexUltrascale+ KU15P au plus près des données

Mais surtout ce Smart SSD intègre un FPGA (Field Programmable Gate Arrays) de chez Xilinx pour effectuer des calculs. Il s’agit en l’occurrence d’un KintexUltrascale+ KU15P, avec 4 Go de DDR4. Pour rappel, AMD a officialisé le rachat de cette société, pour 35 milliards de dollars en action, la finalisation n’est pas attendue avant fin 2021.

Le SmartSSD peut ainsi effectuer directement des calculs sur les données dont il dispose, sans avoir besoin de passer par le CPU de la machine. Le fabricant affirme que cela permet « d’importants gains de performances […] tout en libérant le processeur qui peut gérer plus efficacement d'autres tâches ».

Des améliorations de performances « jusqu’à 10 fois ou plus »

Le FPGA prend en charge la plateforme unifiée Vitis afin de faciliter « la création de nouveaux accélérateurs et leur intégration dans les applications ». Xilinx cite en exemple des fonctionnalités telles que dm-crypt et Virtual Data Optimizer.

De manière générale, la société affirme que le « SmartSSD accélère considérablement les applications gourmandes en données, jusqu’à 10 fois ou plus ». Selon des tests internes, il est par exemple question d’un gain de 2,8x sur les requêtes SQL et d’une réduction de 87 % de l’utilisation du CPU pour du transcodage vidéo.

Plus on ajoute de SmartSSD, plus on dispose de FPGA et plus les gains peuvent être importants. De plus amples détails sont disponibles sur cette page et celle-ci.

Précommande ouverte, pour le tarif on repassera

Des démonstrations ont été proposées durant le Flash Memory Summit 2020 qui vient de se terminer. Les précommandes sont ouvertes, avec une disponibilité prévue pour le mois de janvier. Le tarif n’est pas précisé.

Commentaires (12)

#1

Plus on avance dans l’informatique moderne, plus je réalise qu’on revient aux prémices de celle-ci. Rappelez vous des co-processeurs arithmétiques des débuts.

On commence à ajouter des excroissances à nos CPU pour les libérer de calculs…

(3615malife) Rien à voir, mais en parlant de ça, j’ai des images de l’Amstrad pc1512 de mon père qui me reviennent :p

que de beaux souvenirs sur Gem Paint et l’outil de dessin en langage Basic ^_^

#2

Hum, le problème des FPGA, c’est que ça peut faire une chose très efficacement, mais qu’une seule chose.

Donc si tu développes un accélérateur pour une tache, du coup il faut que tes 3.84To de données soit affectés à cette seule utilité (enfin c’est la compréhension que j’en ai). Donc évidemment ça peut avoir son utilité quand tu es un pro d’un domaine particulier, mais a voir niveau tarif, par rapport à avoir des RAID de NVMe + un plus gros CPU.

Et j’espère leur plateforme Vitis elle simplifie par rapport au VHDL, car ce truc c’est vraiment a pain in the ass…

#3

C’est toujours le cas, ça s’appelle un MAC, c’est juste que c’est gravé avec le reste du CPU sur le même silicium

#4

Je ne sais plus où j’avais vu ça, mais il me semblait qu’il existait déjà des machines avec des FPGA intégrés qui pouvaient être reprogrammés à la volée pour accélérer matériellement la tâche en cours.

En tous cas le gain annoncé est impressionnant, reste à voir si c’est assez ouvert pour que tous les systèmes en profitent.

#5

C’est tout l’intérêt de la partie “FP” du FPGA: ça se reprogramme très vite, de l’ordre de la milliseconde. Du coup on peut très bien imaginer avoir un jeu d’applications pour les opérations les plus gourmandes et une automatisation pour basculer d’un mode à un autre.

#6

Je me trompe peut-être, mais un FPGA, c’est justement reprogrammable (pas forcément rapidement).

Il me semble en effet qu’un FPGA est un cicruit avec plein de porte logique, et on peu le programmer en bloquant ou ouvrant les lignes entre les portes.

De plus, à l’époque que j’avais entendu parler de ça, on m’avait expliqué qu’en plus de coûter un bras, ce n’était pas très efficace, son principale intérêt, c’était pour faire du prototypage de puce.

#7

Le FPGA est l’intermédiaire entre un ASIC et un CPU: ça a une partie de la performance de l’ASIC avec une partie de la programmabilité du CPU.

#8

La programmation du FPGA est rapide. Ce qui est lent c’est la synthèse du programme qui tourne dessus (l’équivalent de la compilation pour un FPGA). Selon la taille du programme et du FPGA, c’est rapidement 1 heure de compilation. Mais une fois que le programme est compilé, c’est très rapide de programmer le FPGA (de l’ordre de la milliseconde). Il y a même des FPGAs qui se peuvent se reprogrammer partiellement pendant l’exécution.

Le principal avantage du FPGA c’est son parallélisme quasi sans limite: selon le problème les FPGAs peuvent être plus efficace que les CPUs/GPUs. Le principal problème c’est la fréquence maximum liée à la technologie utilisé mais aussi à l’application qu’il exécute (chemin critique du circuit programmé).

#9

Ce n’est pas toujours le cas. Si tu utilises une mémoire flash série et que le fpga est gros, cela peut être plus long.

#10

Oui effectivement, je me suis mal exprimé. Je voulais dire “qu’une seule chose à la fois au même moment”

#11

Prochaine étape, réintégrer tous ces circuits dédiés au sein d’une même puce …

Et recommencer

#12

Ça s’appelle une Mac. Pardon, je veux dire que certaines machines Apple ont un FPGA intégré (Mac pro de mémoire).

Sinon y’a pas mal de FPGA en PCIe, mais c’est pas gagné que ça soit utilisé pour les programmer.