C'est parti pour Ampere : lors de sa conférence en ligne de la GTC 2020, Jen Hsun Huang va présenter ce nouveau GPU haut de gamme devant être intégré dans des serveurs... mais aussi décliné à de nombreuses sauces. Une puce géante qui dévoile ses premiers atouts... mais pas encore la totalité de ses secrets.

Cela fait des mois que les rumeurs courent sur la prochaine génération de GPU NVIDIA : Ampere. Elles ont été nombreuses, souvent contradictoires, mais au final, nos prévisions étaient juste : les annonces du jour ne concernent que des produits à destination des professionnels. Les GeForce GTX 3080 Ti* attendront.

Ampere vient donc remplacer Volta (V100), l'A100 dévoilé aujourd'hui ayant tout d'un monstre pour datacenter. Pour NVIDIA, l'enjeu est en effet de garder son avance pour les années à venir, alors qu'AMD opère un retour progressif et va s'attaquer à ce marché avec Navi 2X, pendant qu'Intel prépare son propre GPU Xe qui visera lui aussi les serveurs.

Ampere n'y va pas avec le dos de la cuillère

Le caméléon a donc fait dans la démesure, ajoutant à son architecture quelques nouveautés. Commençons par quelques chiffres : une puce A100 est gravée en 7 nm par TSMC (N7). Elle se compose de pas moins de 54,2 milliards de transistors, regroupés dans un die de 826 mm². La plus grosse puce produite sur ce process selon NVIDIA. Pour rappel, Volta (gravé en 12 nm) mesurait 815 mm².

Le tout se présente sous la forme d'un module SXM4, 40 Go de HBM2 (5120 bits) étant « stackés », atteignant un débit de 1,6 To/s. Le TDP de l'ensemble : 400 watts.

En charge des calculs matriciels, les Tensor Cores d'Ampere sont de troisième génération, après ceux de Volta puis de Turing. Ils gèrent FP64 et un nouveau format de données : TF32. Sorte de Bfloat16 amélioré il combine la précision du FP16 (mantisse de 10 bits) et la largeur du FP32 (exposant de 8 bits).

NVIDIA promet une accélération sans modification du code. Nous manquons encore de détails sur leurs implémentations concrètes (via CUDA, TensorRT, etc.). Nous tenterons d'en savoir plus sous peu.

Le constructeur dit aussi avoir optimisé son architecture pour les matrices creuses (sparsity) doublant l'efficacité lorsque de tels cas se présentent. Ainsi, Ampere serait deux fois plus performant que Volta en FP64, 6/7x sur BERT, jusqu'à 20x en croisant ses nouveaux avantages techniques. Des déclarations qu'il faudra vérifier dans les faits.

Autre ajout qui pourra intéresser certains : il est désormais possible de « découper » un GPU Ampere en 7 instances de GPU. Là aussi, on manque de détails sur l'implémentation concrète et comment cela pourra être exploité. Attendons donc les documentations techniques qui ne manqueront pas d'être publiées. SR-IOV est géré.

Pour le moment, aucune déclinaison PCIe (4.0) n'est annoncée. L'A100 est d'ores et déjà en production, distribué à des clients. La puce sera accessible via de nombreux services Cloud et intégrateurs : Alibaba Cloud, Amazon Web Services (AWS), Atos, Baidu Cloud, Cisco, Dell, Fujitsu, Gigabyte, Google Cloud, H3C, Hewlett Packard Enterprise (HPE), Inspur, Lenovo, Microsoft Azure, Oracle, Quanta/QCT, Supermicro et Tencent Cloud.

A100 : tout pour le calcul

Vous avez remarqué que nous n'avons pas encore parlé de ray tracing et de RT Cores ? C'est normal : il n'y en a pas dans cette première déclinaison d'Ampere. L'A100 est taillé pour le calcul, l'entrainement de réseaux neuronaux et l'inférence, comme la gamme Tesla. RTX reste la chasse gardée de Turing pour le moment, des GeForce et des Quadro.

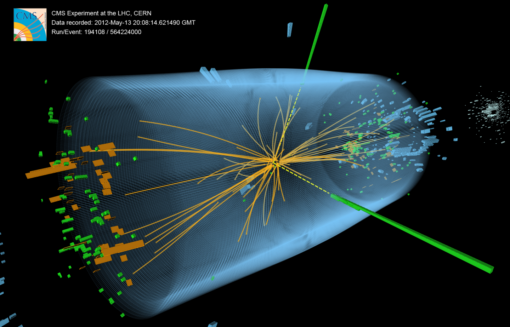

Un GPU A100 compte ainsi pas moins de 108 SM (Streaming Multiprocessors), pour un total de 6 912 CUDA Cores (FP32, 64 par SM), 432 Tensor Cores, 432 unités de texturing et 40 Mo de cache L2. Le tout fonctionne à une fréquence maximale de 1,41 GHz. NVIDIA annonce également 312 TFLOPS (FP16) et 624 TOPS (INT8 ) :

Pour rappel, une V100 SXM2 annonçait 15,7 TFLOPS, contre 16,3 TFLOPS pour une Titan RTX avec 4 608 CUDA Cores mais une fréquence de 1 770 MHz. Un gain de 20 % en puissance de calcul brute, auquel il faudra rajouter les optimisations de l'architecture, mais aussi ses capacités d'interconnexion (NVLink/Switch de 3e génération). Une chose est sûre : NVIDIA garde encore quelques « billes » pour de prochaines annonces.

Notez d'ailleurs que si aucune GeForce n'est pour le moment annoncée, de nombreuses déclinaisons sont déjà lancées. Le SoC Orin bien entendu, qui a déjà été annoncé dans le domaine automobile. Mais aussi EGX pour les solutions de communications avec l'intégration à une carte réseau 2x 100G de Mellanox (qui appartient désormais à NVIDIA), des baies DGX/EGX. Le tout accompagné de nombreuses évolutions des couches logicielles.

Retrouvez la présentation de Jen Hsun Huang ci-dessous :

* Dénomination non contractuelle

Commentaires (9)

#1

C’est d’un joli plat de lasagne que nous sort du four Jen Hsun Huang !

Il renouvelle la solution pour les DC, il déploit sur les solutions réseau (nouveau domaine), prépare sa mise à jour sur l’automobile.

En plus, il montre gentiment qu’il a la plus grosse (puce) et met gentiment la pression sur AMD côté Quadro et RTX… joli.

Après, faudra voir les tarifications appliquées par nVidia sur tout ce petit monde (DC, réseau, automobile) pour espéré voir comment ils souhaitent se positionner.

#2

Pour l’instant, je reste bloqué sur sa collection de spatules. Et bon, une crédence comme ça, ça doit super chiant à nettoyer.

Sinon, ouai, ça semble pas dégueulasse ce qu’il nous sert là.

Gentiment n’est pas forcément le terme le plus adapté. Mais ouai, ça donne la petite claque pour rappeler qu’il n’est pas le roi de la cour des grands pour rien.

#3

il fait ça avec le sourire, c’est gentil

#4

Le tout se présente sous la forme d’un module SXM4, 40 Go de HBM2 (5120 bits) étant « stackés », atteignant un débit de 1,6 To/s. Le TDP de l’ensemble : 400 watts.

Donc Nvidia utilise la technologie CoWos de TSMC ?

#5

Je ne comprends pas trop comment on arrive à “Un gain de 20 % en puissance de calcul brute,”. Pour moi passer de 15,7 TFLOPS à 312 TFLOPS, c’est un gain de 1900% (ie. 20x), pas 20%.

Où est-ce que je me trompe?

#6

Les 15.7⁄16.3 TFLOPS, c’est en FP32, donc à comparer aux 19.5 TFLOPS annoncés aujourd’hui.

#7

Y’a de grandes chances oui :)

Peut être même la version 2 annoncée récemment par TSMC et Broadcom.

#8

J’ai souvenir que certaines puces NVIDIA était utilisées dans les tesla pour la reconnaissance de l’environnement dans le cadre de la conduite autonome au travers de l’intelligence artificielle, est ce que ça sera un domaine d’utilisation d’ampère également ?

#9

Comme dit dans le second article, Orin a déjà été annoncé pour ça il y a quelques mois, avec un GPU intégré Ampere (et des coeurs CPU Arm Hercules)