Samsung dispose désormais de six lignes de productions dans trois usines. La dernière en date, V1, commence à produire en masse des puces gravées en 7 nm, ou moins. Ce n'est qu'un début.

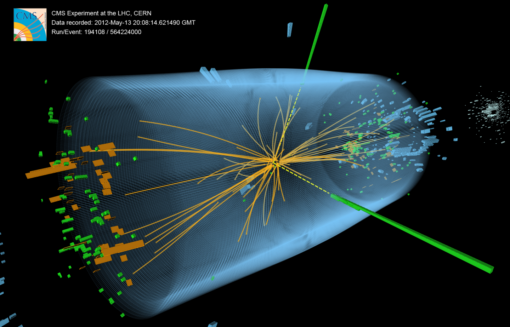

C'est dans son usine de Hwaseong (en Corée du Sud) que Samsung vient de lancer une nouvelle ligne de production, V1, « dédiée à la lithographie EUV » pour des puces gravées en 7 nanomètres ou moins.

Inaugurée en février 2018, elle a débuté la production de wafers durant le second semestre 2019. Le coût total de l’investissement est de 6 milliards de dollars. Les livraisons des premières puces seront réalisées durant ce premier trimestre 2020. La production de masse ayant commencé.

De quoi tripler sa capacité de production en 7 nm et moins d’ici la fin de cette année, le constructeur commençant déjà à produire en 6 nm, visant à termes les 3 nm seulement. Mais pour le moment, aucun calendrier précis n'a été donné pour les prochaines étapes ou même le début de la production de masse.

Au total, Samsung dispose désormais de six lignes de productions : cinq se trouvent en Corée du Sud – deux dans l’usine de Giheung, trois dans celle de Hwaseong – et une dernière aux États-Unis, à Austin. Trois d’entre elles sont capables de graver des puces en 10 nm ou moins.

Commentaires (12)

#1

3nm ??….

Wow… Je croyais qu’il y avait une limite physique à 7 ? Visiblement, c’était pas si gênant… Qui s’interesse à la physique de toute manière ?

#2

6 millions de dollars d’investissement ? ça me semble bien peu, non ?

#3

Oui milliards et pas millions… je vais me fouetter un coup

#4

on saute et on recommence !

#5

mm, µm, nm, pm, …

Pour le coup, pas d’unités impériales !

#6

Est ce que les processeurs supporteront le bug des zero mm ? ou il faut une mise à jour?

#7

Ce sont (malheureusement) des dénominations marketing, la taille minimale des composants et la densité offerte ne correspondent pas à la “finesse de gravure” indiquée.

Par exemple le 10nm de TSMC est similaire au 14nm d’Intel (un peu plus dense) tout comme le 10nm d’Intel est similaire au 7nm de première génération (un peu plus dense).

https://semiwiki.pw/semiconductor-manufacturers/intel/7343-leading-edge-logic-landscape-2018/

#8

Il y a de toutes façons une limite physique à la taille de l’atome, environ 0,1 nm. Apparemment on arrive à continuer à descendre, plus lentement et difficilement, en taille de gravure, avec beaucoup de recherche ; en particulier pour limiter les courants de fuite (effet tunnel par exemple, sauf erreur de ma part), en utilisant des dopages plus sophistiqués et de nouveaux alliages.

#9

Quand je vois ce genre de News, je me dis que l’Europe est totalement à la ramasse :‘(

#10

Comme l’ont dit Norde et OlivierJ, les dénominations des nœuds techno sont juste du marketing, et depuis qq années maintenant. Avant le 22nm d’Intel, en général, les transistors étaient plats. Le problème fut qu’il était quasi-impossible de réduire le nœud 22nm de manière standard. Porte logique qui fait 28nm->porte qui fait 22nm. D’où l’introduction du FinFET qui introduit la 3e dimension dans le transistor.

Bref, tout ça pour dire, de nos jours, la réduction vient plutôt de l’introduction de nouvelles formes de transistor et d’un meilleur contrôle des courants de fuite (qui peut passer par de nouveaux alliages). Pour les dopages, pas vraiment c’est toujours les mêmes.

#11

Tu veux parler de la production même? C’est certes pas grand chose par rapport aux Coréens , TSMC et Intel, mais y’a quand même Global Foundries à Dresde, Intel en Irlande et dans une moindre mesure STMicroelectronics Crolles/Rousset.

Si tu parlais d’usines/entrerprises européennes, là effectivement y’a plus grand chose.

Ah! Voilà les chiffres:

https://en.wikipedia.org/wiki/Semiconductor_industry#/media/File:Who_exported_Electronic_integrated_circuits_in_2016.svg

#12

(merci pour ton commentaire)

Je ne suis pas expert en dopage, mais il y a quand même des évolutions si j’en crois cet article de 2014 ( https://www.lefigaro.fr/sciences/2014/04/20/01008-20140420ARTFIG00169-les-puces-electroniques-flirtent-avec-leurs-limites.php ), et j’ai retrouvé ce à quoi je pensais en parlant de nouveaux dopages, en fait il s’agit des isolants à base de Hafnium, dont Intel s’était mis à parler il y a quelques années.

Extraits (le 2e concerne plutôt le dopage il me semble) :

Pour les isolants, l’oxyde de hafnium est devenu très prisé pour «les petites dimensions, en deçà de 45 nm» [..]

Par ailleurs, l’arséniure de gallium et le germanium trouvent un regain d’intérêt. Déposés à la surface du silicium, ils «permettent d’augmenter la mobilité des porteurs de charge (électrons et “trous”, NDLR) pour les générations de 10 nm et au-dessous»