Comme prévu, Pat Gelsinger a dévoilé hier soir la feuille de route d'Intel pour les quatre prochaines années. Il était plus question de grandes décisions stratégiques que de détails techniques, le fondeur se gardant quelques cartouches pour son évènement de rentrée.

Lorsque nous nous rendions à l'Intel Developer Forum (IDF) il y a une dizaine d'années, il y avait un moment incontournable : celui où Steven L. Smith et Mark Bohr venaient détailler à la presse, en session privée, la feuille de route pour les années à venir et les dernières évolutions dans le domaine de la finesse de gravure.

Après des années d'erreur, Intel relève la tête

Puis l'IDF s'en est allé, tout comme la capacité d'Intel à détailler ses feuilles de route. On connait la suite, et les années sombres où, sous la direction de Brian Krzanich, le fondeur s'est éparpillé plutôt que de préparer l'avenir sur les marchés qui font sa force. Il a laissé AMD et NVIDIA lui tailler des croupières, ARM monter en puissance, etc.

Depuis quelques années néanmoins, la société prépare son retour et travaille d'arrache-pied à différents projets. La modularisation de ses solutions, la réorganisation de sa fonderie, la conception de nouvelles architectures plus innovantes. Il lui faut à la fois rattraper le retard et faire la différence. Avec une force : Intel reste une société solide, tout comme son bilan financier, toujours leader dans de nombreux secteurs.

Tiger Lake, avec son architecture Willow Cove et sa partie graphique Xe, était un tournant. Une génération marquant le lien entre la période « BK » et celle de la nouvelle équipe, qui a décidé de se reprendre en main et de concevoir des solutions plus efficaces. Avec à la clé des solutions diversifiées, que les développeurs peuvent exploiter via OneAPI. Au point qu'Intel lance sa propre gamme de GPU et des cartes graphiques.

Le temps de la reconquête

En 2021, on rentre dans le dur. Cette nouvelle phase est faite d'architectures hybrides, d'exploitation des blocs d'IP intégrables (tant par Intel que ses partenaires), d'ouverture à ARM et RISC-V, de la fonderie à des tiers via IDM 2.0, du passage rapide au 7 nm suivi d'une progression régulière de la finesse de gravure.

- IDM 2.0 : Intel veut devenir un fondeur comme les autres (mais souverain)

- Pat Gelsinger évoque Meteor Lake (7 nm), le retour du Tick-Tock et Intel on

Pour diriger cette nouvelle « ère », le conseil d'administration a choisi un PDG qui connait bien la maison : Pat Gelsinger. Après six mois à réorganiser les équipes, revoir les priorités, présenter les travaux en cours et relancer la machine, il en dit un peu plus sur l'avenir à long terme de la société, feuille de route à l'appui.

Une manière de préparer le terrain pour l'évènement qui doit signer le grand retour de l'IDF, sous un autre nom : Intel on, les 27 et 28 octobre prochains. Le géant de Santa Clara devrait alors être plus concret. Hier soir, il a surtout détaillé les grandes lignes de son projet d'ici 2025 et ses partenariats avec Amazon ou Qualcomm.

Node de gravure : changement de nom....

Première décision, en finir avec le ridicule des dénominations de la finesse de gravure, faite de « +++ » et autres « SuperFin » qui ne veulent rien dire. Intel n'est plus dans sa position de leader incontesté du marché, il lui faut désormais s'adapter à ses concurrents, qui n'ont pas la même manière de traiter le sujet.

La société ne peut plus évoquer la taille des transistors sans se préoccuper de la manière de faire chez Samsung ou TSMC, où les caractéristiques techniques diffèrent. Car oui, il n'y a pas de standard en la matière et le 10 nm d'Intel n'équivaut pas à du 10 nm ailleurs. Retarder artificiellement le passage au 7 nm à coup de « + » n'a pas de sens.

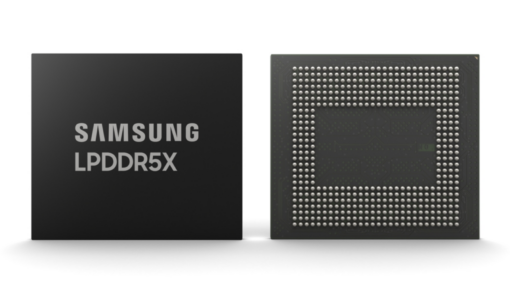

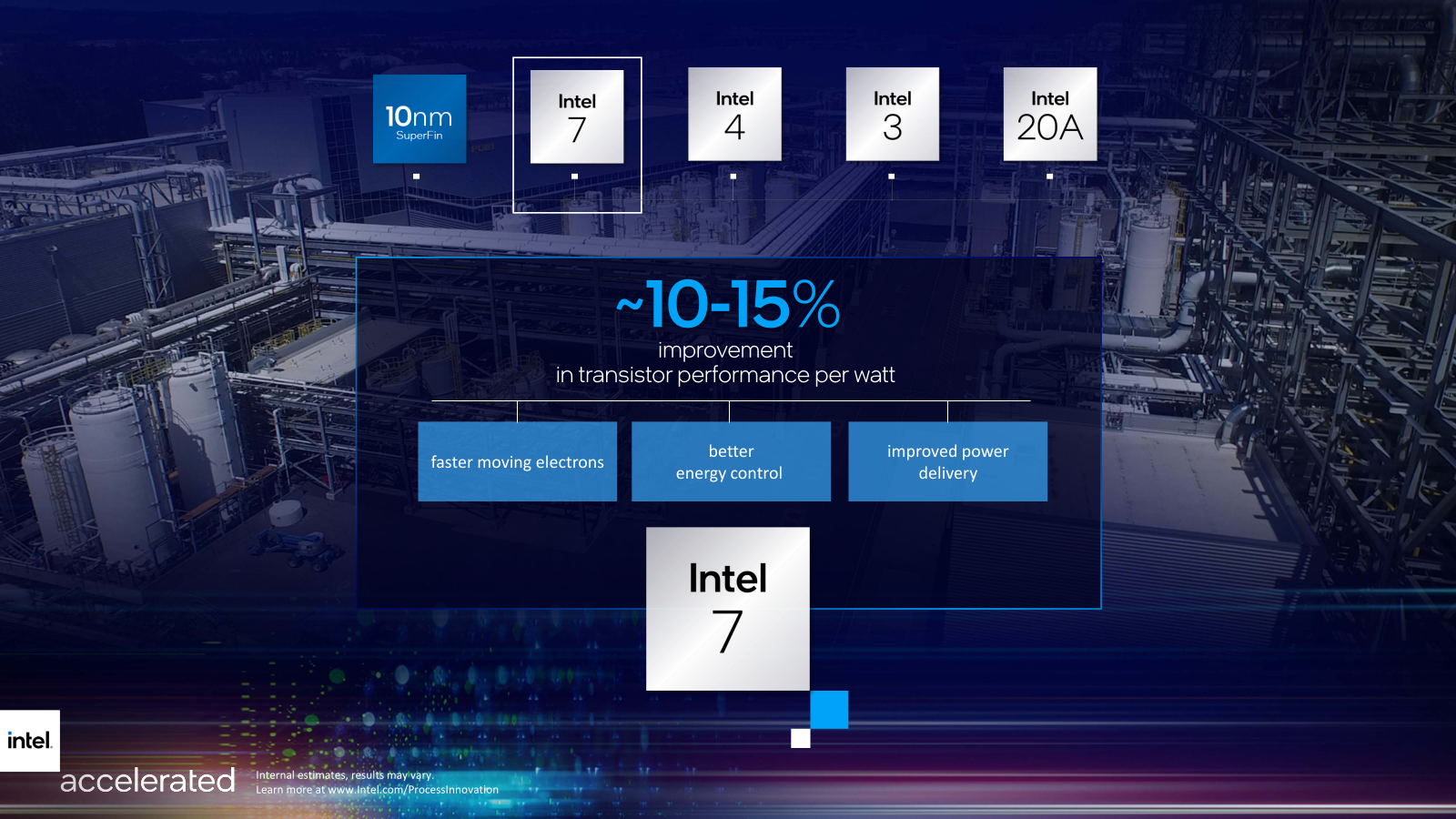

Le 10 nm SuperFin garde donc son nom, mais sa prochaine itération s'appellera « Intel 7 ». Des gains de 10 à 15 % en performances/watt sont attendus via des améliorations (non détaillées) sur les transistors FinFET. L'Intel 7 devrait venir se frotter aux processus en 7 et 5 nm de TSMC.

Elle est désormais en production de masse et servira à la conception d'Alder Lake (grand public) et Sapphire Rapids (Serveurs). Le premier doit être mis sur le marché à travers de premiers modèles pour PC de bureau de la gamme « K » dès la rentrée, le second doit entrer en production dès le premier trimestre 2022.

La gravure en 7 nm devient « Intel 4 ». L'évolution majeure est l'utilisation de la lithographie EUV (longueur d'onde de 13,5 nm contre 193 nm précédemment) dans son ensemble, en partenariat avec IMS et le néerlandais ASML. Un gain de 20 % sur le rapport performances/watt est attendu.

Sa conception est finalisée dans ses grandes lignes, elle sera prête pour la production dans la seconde moitié de 2022. Les premières puces Meteor Lake, qui exploiteront ce procédé, ont été produites (Tape in) il y a peu.

Cette architecture (grand public) est attendue pour 2023, elle sera composée de cœurs, chipsets et GPU (de 96 à à 192 unités de calcul) séparés sur différentes puces interconnectées au sein d'un même packaging, avec un TDP pouvant aller de 5 à 125 watts. Elle sera suivie de Granite Rapids pour les serveurs.

... et cap sur les 0,1 nm

Les travaux sur la finesse de gravure étant un travail de longue haleine, les grandes lignes jusqu'à 2024 sont tracées, la suite étant encore au stade de la R&D. Dès la mi-2023, le fondeur compte passer à Intel 3 avec un gain de 18 % en performances/watt grâce à une amélioration globale de son procédé et une utilisation accrue de la lithographie EUV. Le fondeur évoque aussi une nouvelle bibliothèque plus efficace en termes de densité.

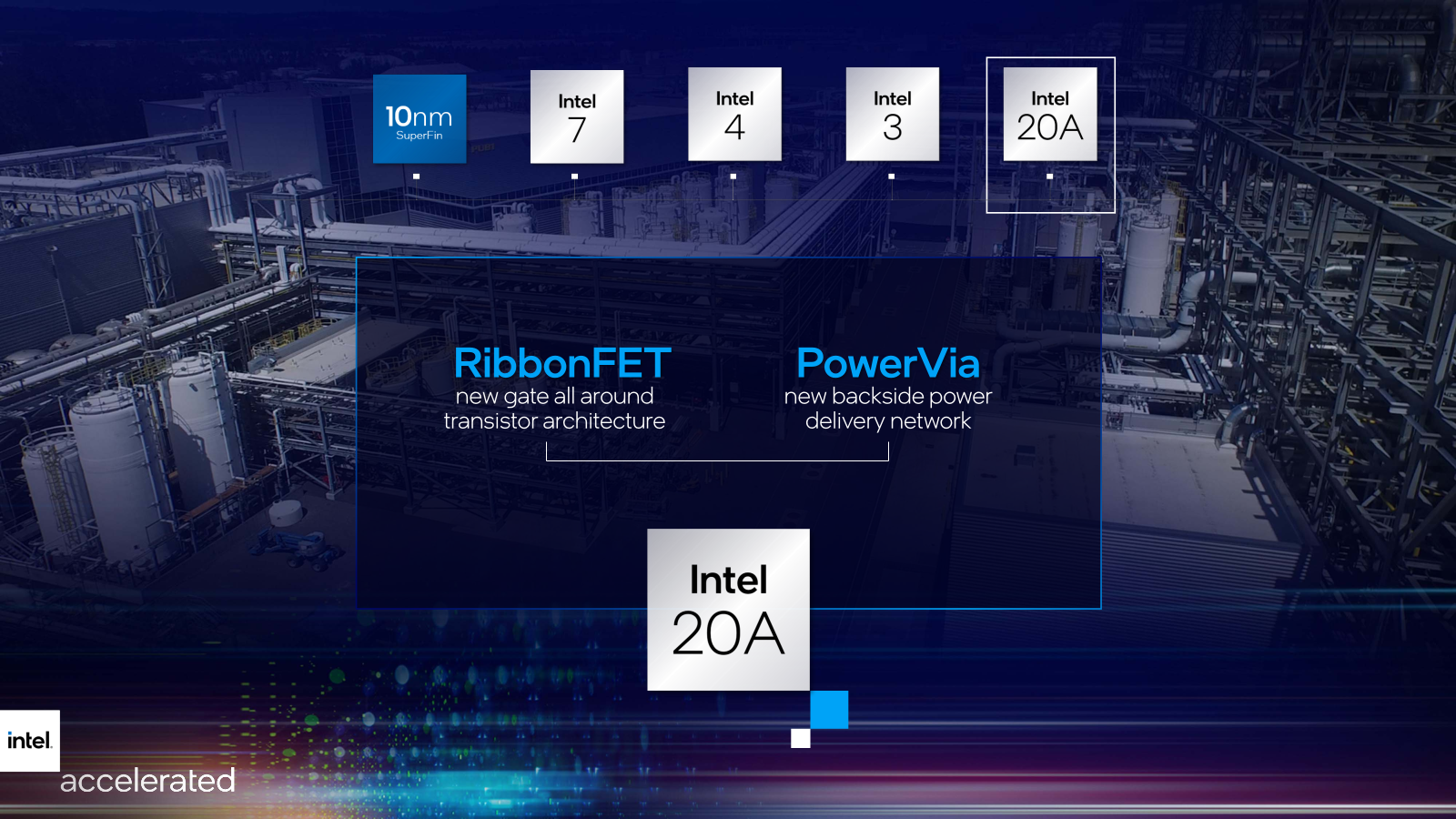

En début d'année suivante, il devrait présenter Intel 20A, qui marquera « l'ère angström » des semi-conducteurs, ce qui désigne une unité équivalant à 0,1 nanomètre. Une manière d'indiquer que l'on se dirigera alors tout droit vers des solutions nous menant sous la barre du 1 nm, grâce à de nouveaux transistors RibonnFET et l'introduction des PowerVia. Le plus grand changement que la société aura connu depuis l'arrivée du FinFET en 2011.

Intel vante ici ses canaux sous forme de rubans entièrement « entourés » par la grille désormais, avec pour résultat un « meilleur contrôle et un courant plus élevé quelle que soit la tension », offrant meilleures performances, mais surtout des designs bien plus denses. La largeur des « rubans » peut d'ailleurs être modifiée pour adapter le fonctionnement à différents besoins selon Intel. Pour rappel, la concurrence travaille à des solutions similaires, connues ailleurs sous le nom de GAAFET et MBCFET chez TSMC et Samsung qui l'évoquent pour le 3 nm.

Les PowerVia sont une nouvelle organisation de la structure générale avec une séparation du transfert des données et de la distribution de l'alimentation qui ne sont désormais plus entremêlés, conçues chacune selon ses besoins propres. Les transistors sont placés entre ces deux couches avec des interconnexions (Nano TSV, Through Silicon Via) 500 fois plus compactes que les solutions actuelles. Là aussi avec la promesse de meilleures performances.

La production en volume sur ce processus est attendue pour 2024, Qualcomm ayant déjà indiqué qu'il l'utilisera pour certaines de ses puces (sans plus de précisions). 18A suivra en 2025. Intel espère alors être revenu au niveau de ses principaux conccurents, tant dans la fonderie que sur le marché des processeurs.

Commentaires (20)

#1

Même si je suis très content d’être passé chez les rouges récemment, c’est cool de voir que Intel semble enfin vraiment réagir. A voir si ça sera suivi dans les faits, mais les annonces sembles promettre une concurrence saine

#2

en partenariat avec IMS et le français ASML

Je ne savais pas qu’ASML était français, Intel oublie de dire comment ils comptent avoir plus de machines EUV c’est TSMC et Samsung qui en ont/en commande le plus

#3

Le 7nm qui s’appelle Intel 4, c’est un peu le retour du P-Rating (mais il a changé de camp !)

#4

My bad, une connerie qui est restée sans modif avant correction. Pour le reste, je n’ai pas souvenir que des fondeurs communiquent publiquement sur leur niveau de commande de telles machines.

Comme dit dans l’article, ce n’est qu’un rattrapage qui était attendu par rapport aux pratiques du reste du marché. On comprend surtout mal pourquoi ça a mis tant de temps à se mettre en place alors qu’Intel (entre autres) est quand même vocal depuis quelques années sur le sujet.

L’important in fine, plutôt le nom marketing donné par les fondeurs, ce sera toujours la densité et l’efficacité énergétique des puces telles qu’implémentées par les constructeurs.

#5

AnandTech présente un tableau de la densité de chaque fondeur, ce qui permet de mieux comprendre ce renommage, qui n’a pour moi pas grand chose à voir avec l’histoire du P-Rating.

Pour une fois je trouve qu’Intel est le seul à être resté sur des termes “justes”, contrairement aux autres, qui ont fait du marketing.

#6

L’inconnue est de savoir combien de machine EUV ASML est capable d’en produire chaque année pour fournir tous les fondeurs qui en ont besoin

#7

La réponse intéressante est plutôt en bout de chaîne : quand Intel pourra produire en masse dans son process full EUV (2022⁄2023) et avec quelle densité/efficacité (on verra). Tout le reste tiendra, au mieux, de l’extrapolation sur des informations partielles.

#8

Une cinquantaine de machines/an à priori https://twitter.com/nerdtechgasm/status/1419091938385432578

#9

C’est quoi de “block d’IP integrables? (Pd: je sais ce qu’est une IP)

#10

IP ici, c’est Intellectual Property, pas Internet Protocol.

Il s’agit d’intégrer un bloc conçu ailleurs que chez Intel.

#11

Intéressant. Au début, j’ai cru lire une erreur de typo avec 13.5 nm… mais non ! C’est clairement cohérent pour des très petits motifs, mais le saut est relativement violent depuis 193nm (même si les sources UV de très courtes longueurs d’onde avec un bon niveau de puissance, ca ne se trouve pas comme ca !)

Intel qui se bouge un peu les fesses, ca ne fera pas de mal à personne !

#12

Non, rendre les solutions d’Intel modulaires sous la forme dun catalogue d’IP à commercialiser via IDM 2.0 (ou à intégrer dans les nouvelles archis)

#13

Une façon de lutter contre ARM, mais avec du x86 ?

#14

Bah tout de suite ça a du sens, merci

#15

C’est un peu le pendant “micro-électronique” d’une librairie déja compilée. Tu ne sais pas comment elle est réalisée en terme de câblage des transistors (ou des fonctions logiques, voire du code comportemental qui la décrit - VHDL, System-C etc), mais tu sais comment ce bloc communique avec l’extérieur, à quelle vitesse, les opérations qu’il peut faire. L’avantage, c’est un peu donnant donnant : celui qui a concu le bloc ne le fait qu’une fois, et peut le réutiliser à volonté, l’améliorer, l’inclure dans d’autres projets. Celui qui utilise un bloc IP n’a pas besoin de se poser la question de comment elle fonctionne, sans connaitre les “petits secrets” de celui qui l’a développée.

#16

#17

Il y a des petites choses à considérer ; d’abord quand un fondeur parle de 7nm ou 4nm cette matrice ne s’applique (pas) plus à la totalité de la puce, mais à certaines zones de fortes densités. De plus cette mesure considère le transistor en vue du dessus de la puce ; une petite rotation de la porte (transistor) et hop c’est moins grand. Mais soyons bon joueur. Par contre à 20Å, 200pm, comment fait-on, c’est le diamètre de covalence d’un atome de silicium (Si) et je crois avoir appris qu’une couche mononucléaire d’un conducteur ne conduit pas ?! Qui m’explique, j’ai fait une faute d’épinard (10˟) ?

#18

Tu n’es pas bien loin : le rayon atomique du Si, c’est 0.111 nm, soit 1.11 A. Il reste encore un peu de place pour caser quelques atomes, mais clairement, on tend vers des régimes de fonctionnement balistiques qui n’ont plus grand chose à voir avec le fonctionnement des transistors de qq nm de largeur de canal.

#19

Je veux bien quelques explications justement car selon moi, il s’agit d’une limite physique et donc avec autre chose qu’un ensemble de transistor ?

#20

Encore du marketing bien grossier, il y a 0 deal ni avec Qualcomm ni avec Amazon, Qualcomm évalue juste les technos d’Intel et Amazon est loin de faire produire chez Intel: https://twitter.com/dylan522p/status/1420846536565661699