Micron commence à produire de nouvelles puces tout-en-un, intégrant 8 ou 12 Go de LPDDR5, 128 ou 256 Go de stockage NAND et un contrôleur UFS 3.1. L’objectif est de réduire au maximum l’encombrement au sein d'appareils mobiles comme les smartphones.

En février, lors de l’expédition de ses premières puces de LPDDR5, Micron avait annoncé la couleur : des modules UFS-Based MCP (uMCP) 5 suivraient. Prévus pour la première moitié de 2020, ils sont finalement un peu en retard.

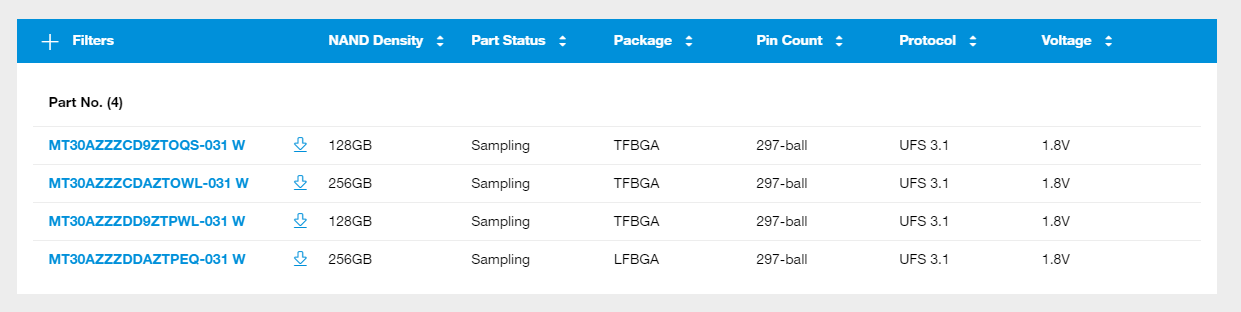

Ils sont désormais prêt pour la production de masse, intégrant de la LPDDR5 (contre de la LPDDR4 pour les uMCP4), de la NAND et un contrôleur UFS 3.1 (Universal Flash Storage), . Les puces sont au format TFBGA (Thin Profile Fine Pitch Ball Grid Array) avec 297 points de contact. Quatre déclinaisons sont évoquées :

- 128 Go NAND et 8 Go de LPDDR5

- 128 Go NAND et 12 Go de LPDDR5

- 256 Go NAND et 8 Go de LPDDR5

- 256 Go NAND et 12 Go de LPDDR5

La LPDDR5 est annoncée à 6,4 Gb/s, mais améliore surtout de 20 % l’efficacité énergétique comparée à la LPDDR4, de quoi améliorer l’autonomie des smartphones selon le constructeur. Le passage à l’UFS 3.1 permettrait de gagner 20 % (par rapport à USF 2.1) sur les taux de transfert selon fabricant.

Des versions de 512 Go sont annoncées, mais aucune disponibilité n’est précisée pour le moment.

Commentaires (4)

#1

Je comprends sûrement mal mais… 6.4 Gb/s ? Ça veut dire qu’une puce de LPDDR5 va à 800 Mo/s ? Ça me paraît extrêmement lent pour de la RAM non ?

#2

Effectivement c’est assez confu dans l’article (et dans le communiqué de Micron), mais différentes pages (ici ou là) ont l’air de s’accorder sur le fait que ça soit 6.4Gb/s par broche (donc 6.4GT/s, si on veut utiliser la bonne unité).

La LPDDR4 est donnée pour 4.2GT/s, et jusqu’à 2.1GT/s pour la LPDDR3.

#3

Je suis surpris par la différence avec la RAM “desktop”, mais il faut bien que la différence de conso vienne de quelque part et si c’est pas sur la quantité, c’est sur le débit.

#4

De ce que j’ai compris, ce n’est pas 6,4 Gb/s mais 6,4 GT/s, le T voulant dire transfert. Par exemple, Samsung a annoncé une puce de 16 Go avec une vitesse de 6,4 GT/s et indique qu’elle pourra transférer 51,2 Go/s. Cela signifie que chaque transfert fait 8 octet (soit 64 bits).

On trouve souvent des articles parlant de 6,4 Gb/s (ou 6400Mb/s) mais je suppose que comme le dit Atchisson, c’est par broche et que donc dans ce cas, il y a 64 broches.

Mais je me trompe pet-être. C’est sous toute réserve après avoir croisé quelques informations.