Malgré la procédure de rachat en cours, ARM continue d'avancer et présente ses évolutions dans le domaine des datacenters. On a droit à deux nouvelles plateformes Neoverse : N2 et V1. Cette dernière veut aller encore un peu plus loin en termes de performances. Jusqu'à se rapprocher de x86 ?

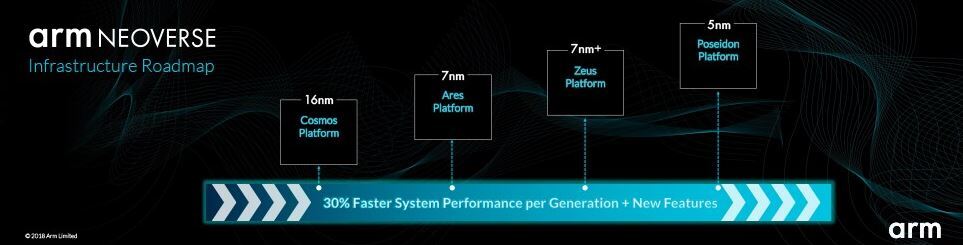

Fin 2018, ARM dévoilait son initiative Neoverse devant lui permettre de partir à la conquête du monde des serveurs. Un complément aux cœurs Cortex qui se focalisent sur la mobilité, notamment les smartphones.

Neoverse et Graviton : session de rattrapage

C'est ce qui a permis à Amazon Web Services (AWS) de proposer ses propres SoC maison, Graviton, ils se basaient alors sur la plateforme Cosmos exploitant du Cortex-A72. En février 2019 ARM passait au 7 nm avec sa plateforme Neoverse N1 – nom de code Ares – présentée comme 60 % plus performante.

Amazon suivait là encore le mouvement avec son processeur Graviton2 qui « offrent une avancée majeure en matière de performances et de capacités par rapport aux processeurs AWS Graviton de première génération ».

Neoverse N2 : 40 % de mieux, PCIe 5.0 et HBM3

Aujourd’hui, ARM passe donc à la seconde génération de sa plateforme Neoverse avec le N2 – nom de code Perseus – qui se veut toujours aussi efficace mais avec des performances en hausse de 40 % par rapport à N1. Le PCIe 5.0 est également pris en charge, tout comme la DDR5, la future mémoire HBM3 , CCIX 2.0 et bFloat16.

Bref, ce sont les prochaines plateformes d'AMD (Zen 4) et Intel (Sapphire Rapids) qui sont visées, devant elles aussi passer à des versions des différents standards dans le courant de l'année prochaine. La finesse de gravure sera de 5 nm. D’ici là, NVIDIA aura peut-être bouclé le rachat d’ARM.

Neoverse V1 : 50 % de performances en plus, SVE

L'entreprise profite de cette mise à jour de sa feuille de route pour évoquer la nouvelle série V. Son but est davantage de proposer des performances brutes plus élevées qu’un bon ratio performances/watt. Pour résumer, Neoverse V1 serait au monde du datacenter ce que le Cortex-X1 serait à celui de la mobilité.

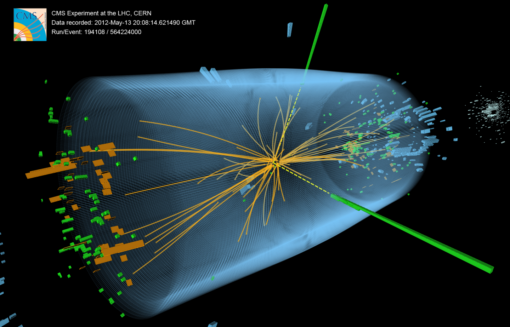

Neoverse V1– Zeus – doit ainsi arriver sous peu et se placer au-dessus de Neoverse N2 puisque les performances sont en hausse de 50 %. Les instructions SVE (Scalable Vector Extensions) sont gérées, « apportant ainsi un énorme potentiel pour des marchés tels que le cloud haute performance, le calcul intensif et l'apprentissage automatique ».

Pour les développeurs, des explications et des détails techniques sont disponibles dans ce billet de blog dédié à SVE et Neoverse V1. Il est d'ores et déjà question de standards de prochaine génération avec de la DDR5, de la mémoire HBM2e et CCIX 1.1. La finesse de gravure est « 7/5 nm » sans plus de détails.

Poseidon à partir de 2022 avec PCIe 5.0 ou 6.0

De nouvelles plateformes – nom de code Poseidon – sont attendues à partir de 2022. Le fabricant prévoit de passer éventuellement au PCIe 6.0 – qui devrait être finalisée en 2021, en doublant encore les débits par rapport à PCIe 5.0 – et sur la prochaine génération de CCIX. Les performances devraient grimper de 30 % environ.

Commentaires (4)

#1

parti comme ça, et entre les mains de Nvidia, ya moyen que les SoC ARM deviennent vraiment des brutes

#2

Oui, après faudra voir avec quel coût/TDP

#3

Ne pas oublier que ARM a travaillé avec Fujitsu sur l’élaboration du SOC A64FX utilisé dans le supercalculateur FUGAKU. Et cela a conduit a l’utilisation de HBM2 et de l’implémentation des instructions SVE en 512 bits.

#4

On en a même déjà parlé ;)